© 1999 Fairchild Semiconductor Corporation DS010637.prf

www.fairchildsemi.com

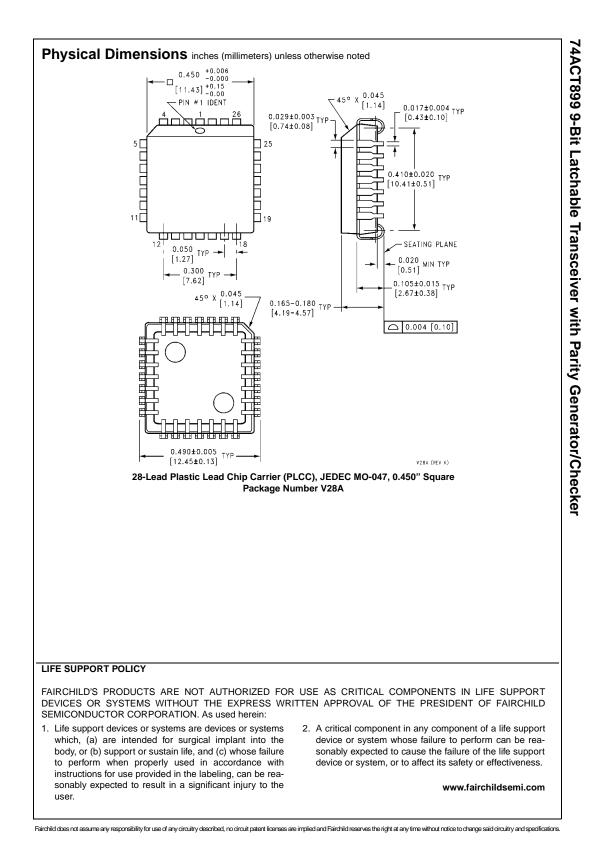

#### **Pin Descriptions**

|                                | -                                                                                  |

|--------------------------------|------------------------------------------------------------------------------------|

| Pin Names                      | Description                                                                        |

| A <sub>0</sub> -A <sub>7</sub> | A Bus Data Inputs/Data Outputs                                                     |

| B <sub>0</sub> -B <sub>7</sub> | B Bus Data Inputs/Data Outputs                                                     |

| APAR, BPAR                     | A and B Bus Parity Inputs                                                          |

| ODD/EVEN                       | ODD/EVEN Parity Select,<br>Active LOW for EVEN Parity                              |

| GBA, GAB                       | Output Enables for A or B Bus,<br>Active LOW                                       |

| SEL                            | Select Pin for Feed-Through or Generate<br>Mode, LOW for Generate Mode             |

| LEA, LEB                       | Latch Enables for A and B Latches,<br>HIGH for Transparent Mode                    |

| ERRA, ERRB                     | Error Signals for Checking Generated<br>Parity with Parity In, LOW if Error Occurs |

#### **Functional Description**

The ACT899 has three principal modes of operation which are outlined below. These modes apply to both the A-to-B and B-to-A directions.

- Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEB (LEA) is HIGH and the Mode Select (SEL) is LOW, the parity generated from B[0:7] (A[0:7]) can be checked and monitored by ERRB (ERRA).

- Bus A (B) communicates to Bus B (A) in a feed-through mode if <u>SEL</u> is HIGH. Parity is still generated and checked as <u>ERRA</u> and <u>ERRB</u> in the feed-through mode (can be used as an interrupt to signal a data/parity bit error to the CPU).

- Independent Latch Enables (LEA and LEB) allow other permutations of generating/checking (see Function Table).

| Functio | n Table |

|---------|---------|

|         |         |

| Inputs |     |     | 5   |     | Operation                                                                                                                                                                                                                              |  |  |  |  |

|--------|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GAB    | GBA | SEL | LEA | LEB |                                                                                                                                                                                                                                        |  |  |  |  |

| Н      | Н   | Х   | Х   | Х   | Busses A and B are 3-STATE.                                                                                                                                                                                                            |  |  |  |  |

| Η      | L   | L   | L   | Н   | Generates parity from B[0:7] based on O/E (Note 1). Generated parity $\rightarrow$ APAR. Generated parity checked against BPAR and output as ERRB.                                                                                     |  |  |  |  |

| Η      | L   | L   | Н   | Н   | nerates parity from B[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ APAR. Generative checked against BPAR and output as ERRB. Generated parity also fed by bugh the A latch for generate/check as ERRA.              |  |  |  |  |

| Н      | L   | L   | Х   | L   | Generates parity from B latch data based on O/E. Generated parity $\rightarrow$ APAR. Generated parity checked against latched BPAR and output as ERRB.                                                                                |  |  |  |  |

| Н      | L   | Н   | Х   | Н   | BPAR/B[0:7] $\rightarrow$ APAR/A0:7] Feed-through mode. Generated parity checked against BPAR and output as ERRB.                                                                                                                      |  |  |  |  |

| Н      | L   | Н   | Н   | Н   | $BPAR/B[0:7] \to APAR/A[0:7]$                                                                                                                                                                                                          |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against BPAR and output as $\overline{\text{ERRB}}$ . Generated parity also fed back through the A latch for generate/check as $\overline{\text{ERRA}}$ .                                  |  |  |  |  |

| L      | Н   | L   | Н   | L   | Generates parity for A[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against APAR and output as $\overline{ERRA}$ .                                                                   |  |  |  |  |

| L      | Н   | L   | Н   | Н   | Generates parity from A[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against APAR and output as ERRA. Generated parity also fed back through the B latch for generate/check as ERRB. |  |  |  |  |

| L      | Н   | L   | L   | Х   | Generates parity from A latch data based on O/E. Generated parity $\to$ BPAR. Generated parity checked against latched APAR and output as ERRA .                                                                                       |  |  |  |  |

| L      | н   | н   | н   | L   | $APAR/A[0:7] \rightarrow BPAR/B[0:7]$                                                                                                                                                                                                  |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output as ERRA                                                                                                                                                            |  |  |  |  |

| L      | Н   | н   | Н   | Н   | $APAR/A[0:7] \rightarrow BPAR/B[0:7]$                                                                                                                                                                                                  |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output as $\overline{\text{ERRA}}$ . Generated parity also fed back through the B latch for generate/check as $\overline{\text{ERRB}}$ .                                  |  |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

L = LOW Voltage Level X = Immaterial

Note 1: O/E = ODD/EVEN

www.fairchildsemi.com

www.fairchildsemi.com

4

www.fairchildsemi.com

6

### Absolute Maximum Ratings(Note 2)

| Supply Voltage (V <sub>CC</sub> )                     | -0.5V to +7.0V                  |         |

|-------------------------------------------------------|---------------------------------|---------|

| DC Input Diode Current (IIK)                          |                                 | F       |

| $V_{I} = -0.5V$                                       | –20 mA                          | (       |

| $V_I = V_{CC} + 0.5V$                                 | +20 mA                          |         |

| DC Input Voltage (VI)                                 | $-0.5V$ to $V_{CC} + 0.5V$      |         |

| DC Output Diode Current (I <sub>OK</sub> )            |                                 |         |

| $V_{O} = -0.5V$                                       | –20 mA                          |         |

| $V_{O} = V_{CC} + 0.5V$                               | +20 mA                          |         |

| DC Output Voltage (V <sub>O</sub> )                   | –0.5V to V <sub>CC</sub> + 0.5V |         |

| DC Output Source                                      |                                 |         |

| or Sink Current (I <sub>O</sub> )                     | ±50 mA                          |         |

| DC V <sub>CC</sub> or Ground Current                  |                                 | N<br>to |

| per Output Pin (I <sub>CC</sub> or I <sub>GND</sub> ) | ±50 mA                          | 0       |

| Storage Temperature (T <sub>STG</sub> )               | -65°C to +150°C                 | S       |

| DC Latch-Up Source or                                 |                                 | 10      |

|                                                       |                                 |         |

Sink Current Junction Temperature (T<sub>J</sub>)

Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )           | 4.5V to 5.5V                   |

|---------------------------------------------|--------------------------------|

| Input Voltage (V <sub>I</sub> )             | 0V to $V_{CC}$                 |

| Output Voltage (V <sub>O</sub> )            | 0V to $V_{CC}$                 |

| Operating Temperature (T <sub>A</sub> )     | $-40^\circ C$ to $+85^\circ C$ |

| Minimum Input Edge Rate $\Delta V/\Delta t$ | 125 mV/ns                      |

| V <sub>IN</sub> from 0.8V to 2.0V           |                                |

| V <sub>CC</sub> @ 4.5V, 5.5V                |                                |

74ACT899

±300 mA 140°C

Note 2: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT™ circuits outside databook specifications.

## **DC Electrical Characteristics**

| Symbol           | Parameter                      | V <sub>cc</sub> | <b>T</b> <sub>A</sub> = | + <b>25°C</b> | $\textbf{T}_{\textbf{A}}=-\textbf{40}^{\circ}\textbf{C} \text{ to } +\textbf{85}^{\circ}\textbf{C}$ | Units | Conditions                           |  |

|------------------|--------------------------------|-----------------|-------------------------|---------------|-----------------------------------------------------------------------------------------------------|-------|--------------------------------------|--|

|                  |                                | (V)             | Typ Gu                  |               | uaranteed Limits                                                                                    |       |                                      |  |

| V <sub>IH</sub>  | Minimum HIGH Level             | 4.5             | 1.5                     | 2.0           | 2.0                                                                                                 | V     | $V_{OUT} = 0.1V$                     |  |

|                  | Input Voltage                  | 5.5             | 1.5                     | 2.0           | 2.0                                                                                                 |       | or $V_{CC} - 0.1V$                   |  |

| VIL              | Maximum LOW Level              | 4.5             | 1.5                     | 0.8           | 0.8                                                                                                 | V     | V <sub>OUT</sub> = 0.1V              |  |

|                  | Input Voltage                  | 5.5             | 1.5                     | 0.8           | 0.8                                                                                                 |       | or $V_{CC} - 0.1V$                   |  |

| V <sub>OH</sub>  | Minimum HIGH Level             | 4.5             | 4.49                    | 4.4           | 4.4                                                                                                 | V     | I <sub>OUT</sub> = -50 μA            |  |

|                  | Output Voltage                 | 5.5             | 5.49                    | 5.4           | 5.4                                                                                                 |       |                                      |  |

|                  |                                |                 |                         |               |                                                                                                     |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |  |

|                  |                                | 4.5             |                         | 3.86          | 3.76                                                                                                | V     | $I_{OH} = -24 \text{ mA}$            |  |

|                  |                                | 5.5             |                         | 4.86          | 4.76                                                                                                |       | $I_{OH} = -24 \text{ mA}$ (Note 3)   |  |

| V <sub>OL</sub>  | Maximum LOW Level              | 4.5             | 0.001                   | 0.1           | 0.1                                                                                                 | V     | I <sub>OUT</sub> = 50 μA             |  |

|                  | Output Voltage                 | 5.5             | 0.001                   | 0.1           | 0.1                                                                                                 |       |                                      |  |

|                  |                                |                 |                         |               |                                                                                                     |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |  |

|                  |                                | 4.5             |                         | 0.36          | 0.44                                                                                                | V     | I <sub>OL</sub> = 24 mA              |  |

|                  |                                | 5.5             |                         | 0.36          | 0.44                                                                                                |       | I <sub>OL</sub> = 24 mA (Note 3)     |  |

| I <sub>IN</sub>  | Maximum Input                  | 5.5             |                         | ±0.1          | ±1.0                                                                                                | μΑ    | $V_I = V_{CC}, GND$                  |  |

|                  | Leakage Current                |                 |                         |               |                                                                                                     |       |                                      |  |

| I <sub>OZ</sub>  | Maximum 3-STATE                | 5.5             |                         | ±0.5          | ±5.0                                                                                                | μA    | $V_I = V_{IL}, V_{IH}$               |  |

|                  | Leakage Current                |                 |                         |               |                                                                                                     |       | $V_O = V_{CC}$ , GND                 |  |

| ICCT             | Maximum I <sub>CC</sub> /Input | 5.5             | 0.6                     |               | 1.5                                                                                                 | mA    | $V_I = V_{CC} - 2.1V$                |  |

| I <sub>OLD</sub> | Minimum Dynamic                | 5.5             |                         |               | 75                                                                                                  | mA    | V <sub>OLD</sub> = 1.65V Max         |  |

| IOHD             | Output Current (Note 4)        | 5.5             |                         |               | -75                                                                                                 | mA    | V <sub>OHD</sub> = 3.85V Min         |  |

| I <sub>CC</sub>  | Maximum Quiescent              | 5.5             |                         | 8.0           | 80.0                                                                                                | μA    | $V_{IN} = V_{CC}$                    |  |

|                  | Supply Current                 |                 |                         |               |                                                                                                     |       | or GND                               |  |

Note 3: Maximum of 9 outputs loaded; thresholds on input associated with output under test.

Note 4: Maximum test duration 2.0 ms, one output loaded at a time.

| 6  |

|----|

| õ  |

| ົບ |

| Ā  |

| 74 |

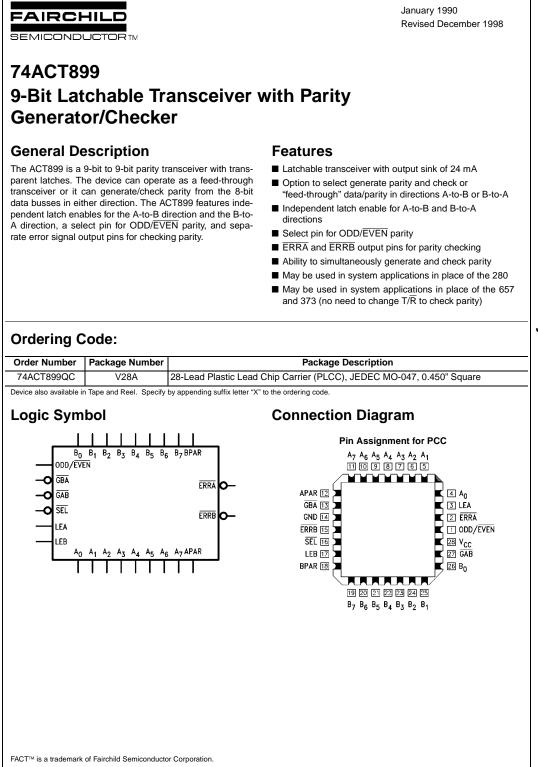

# AC Electrical Characteristics

|                  |                                                                     | V <sub>cc</sub> |                       | $T_A = +25^{\circ}C$ |      | T <sub>A</sub> = -40° | C to +85°C |       | T         |

|------------------|---------------------------------------------------------------------|-----------------|-----------------------|----------------------|------|-----------------------|------------|-------|-----------|

| Symbol           | Parameter                                                           | (V)             | $C_L = 50 \text{ pF}$ |                      |      | $C_L = 50 \ pF$       |            | Units | Fig. No.  |

|                  |                                                                     | (Note 5)        | Min                   | Тур                  | Max  | Min                   | Max        |       | -         |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.5                   | 7.5                  | 11.5 | 2.5                   | 12.0       | ns    | Figure 1  |

| t <sub>PHL</sub> | A <sub>n</sub> , B <sub>n</sub> to B <sub>n</sub> , A <sub>n</sub>  |                 |                       |                      |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 1.5                   | 6.0                  | 8.5  | 1.5                   | 9.0        | ns    | Figure 1  |

| t <sub>PHL</sub> | APAR, BPAR to BPAR, APAR                                            |                 |                       |                      |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.5                   | 8.5                  | 12.0 | 2.5                   | 12.5       | ns    | Figure 2  |

| t <sub>PHL</sub> | A <sub>n</sub> , B <sub>n</sub> to BPAR, APAR                       |                 |                       |                      |      |                       |            |       |           |

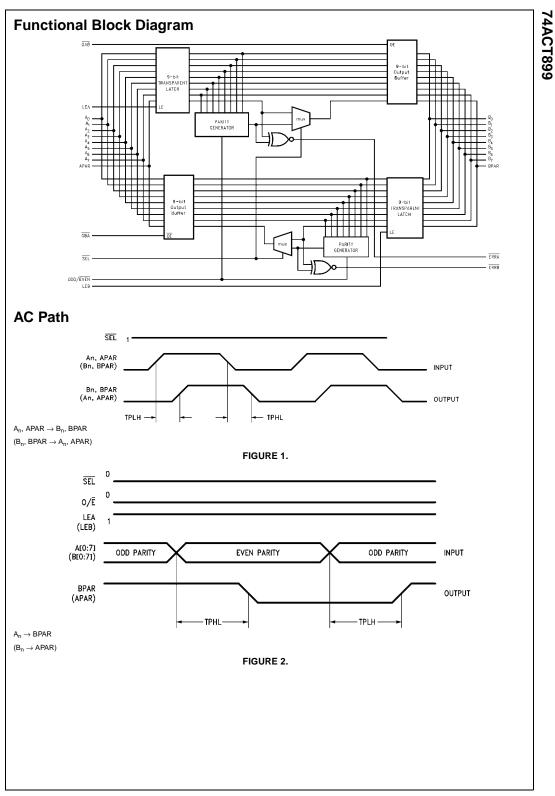

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.0                   | 8.0                  | 11.5 | 2.0                   | 12.0       | ns    | Figure 3  |

| t <sub>PHL</sub> | A <sub>n</sub> , B <sub>n</sub> to ERRA, ERRB                       |                 |                       |                      |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.0                   | 8.0                  | 11.5 | 2.0                   | 12.0       | ns    | Figure 4  |

| t <sub>PHL</sub> | ODD/EVEN to ERRA, ERRB                                              |                 |                       |                      |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.5                   | 8.0                  | 11.5 | 2.5                   | 12.0       | ns    | Figure 5  |

| t <sub>PHL</sub> | ODD/EVEN to APAR, BPAR                                              |                 |                       |                      |      |                       |            |       |           |

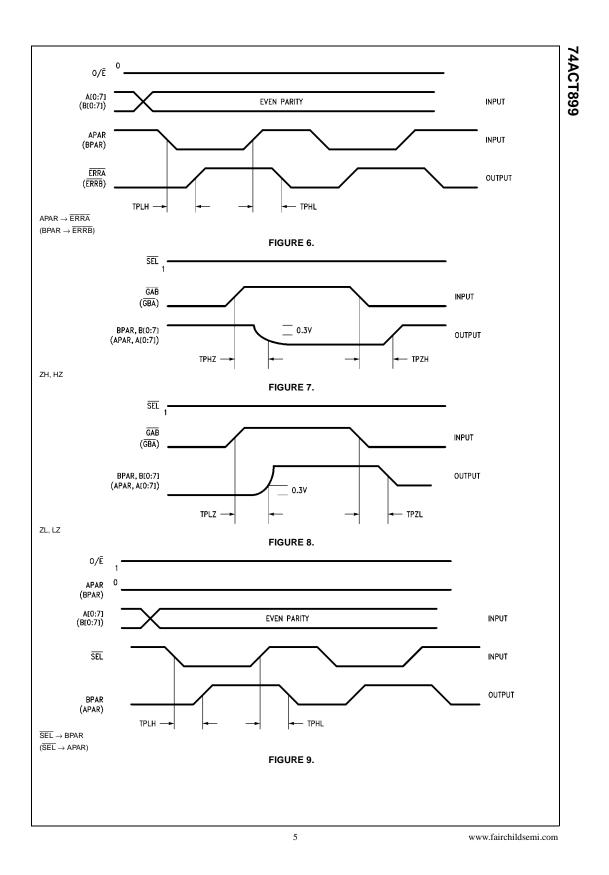

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 1.5                   | 7.5                  | 10.5 | 1.5                   | 11.5       | ns    | Figure 6  |

| t <sub>PHL</sub> | APAR, BPAR to ERRA, ERRB                                            |                 |                       |                      |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 1.5                   | 6.5                  | 9.0  | 1.5                   | 9.5        | ns    | Figure 9  |

| t <sub>PHL</sub> | SEL to APAR, BPAR                                                   |                 |                       |                      |      |                       |            |       |           |

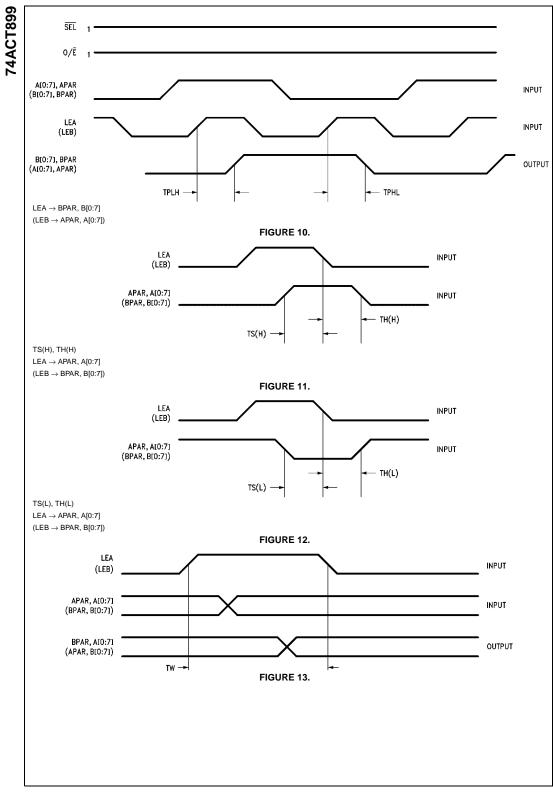

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.5                   | 7.0                  | 10.5 | 2.5                   | 11.0       | ns    | Figure 10 |

| t <sub>PHL</sub> | LEB to A <sub>n</sub> , B <sub>n</sub>                              |                 |                       |                      |      |                       |            |       | Figure 11 |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.0                   | 8.0                  | 11.5 | 2.0                   | 12.0       | ns    | Figure 10 |

| t <sub>PHL</sub> | LEA to APAR, BPAR                                                   |                 |                       |                      |      |                       |            |       | Figure 11 |

| t <sub>PLH</sub> | Propagation Delay                                                   | 5.0             | 2.5                   | 8.0                  | 11.5 | 2.5                   | 12.0       | ns    | Figure 12 |

| t <sub>PHL</sub> | LEA, LEB to ERRA, ERRB                                              |                 |                       |                      |      |                       |            |       |           |

| t <sub>PZH</sub> | Output Enable Time                                                  | 5.0             | 2.5                   | 7.0                  | 10.5 | 2.5                   | 11.0       | ns    | Figure 7  |

| t <sub>PZL</sub> | $\overline{\text{GBA}}$ or $\overline{\text{GAB}}$ to $A_n$ , $B_n$ |                 |                       |                      |      |                       |            |       | Figure 8  |

| t <sub>PZH</sub> | Output Enable Time                                                  | 5.0             | 1.5                   | 6.0                  | 9.0  | 1.5                   | 9.5        | ns    | Figure 7  |

| t <sub>PZL</sub> | GBA or GAB to BPAR or APAR                                          |                 |                       |                      |      |                       |            |       | Figure 8  |

| t <sub>PHZ</sub> | Output Disable Time                                                 | 5.0             | 1.5                   | 6.5                  | 9.5  | 1.5                   | 9.5        | ns    | Figure 7  |

| t <sub>PHL</sub> | $\overline{\text{GBA}}$ or $\overline{\text{GAB}}$ to $A_n$ , $B_n$ |                 |                       |                      |      |                       |            |       | Figure 8  |

| t <sub>PHZ</sub> | Output Disable Time                                                 | 5.0             | 1.5                   | 6.5                  | 9.5  | 1.5                   | 9.5        | ns    | Figure 7  |

| t <sub>PLZ</sub> | GBA or GAB to BPAR, APAR                                            |                 |                       |                      |      |                       |            |       | Figure 8  |

Note 5: Voltage Range 5.0 is  $5.0V \pm 0.5V$ .

# **AC Operating Requirements**

| Symbol         | Parameter                                         | v <sub>cc</sub><br>(V) | T <sub>A</sub> = +25°C<br>C <sub>L</sub> = 50 pF | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$<br>$C_L = 50 \text{ pF}$ | Units | Fig. No.  |

|----------------|---------------------------------------------------|------------------------|--------------------------------------------------|------------------------------------------------------------------------|-------|-----------|

|                |                                                   | (Note 6)               | Guarantee                                        |                                                                        |       |           |

| t <sub>s</sub> | Setup Time, HIGH or LOW                           | 5.0                    | 3.0                                              | 3.0                                                                    | ns    | Figure 11 |

|                | A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB |                        |                                                  |                                                                        |       | Figure 12 |

| t <sub>H</sub> | Hold Time, HIGH or LOW                            | 5.0                    | 1.5                                              | 1.5                                                                    | ns    | Figure 11 |

|                | A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB |                        |                                                  |                                                                        |       | Figure 12 |

| t <sub>W</sub> | Pulse Width for LEB, LEA                          | 5.0                    | 4.0                                              | 4.0                                                                    | ns    | Figure 13 |

Note 6: Voltage Range  $5.0 = 5.0V \pm 0.5V$ .

## Capacitance

| Symbol          | Parameter                     | Тур | Units | Conditions      |

|-----------------|-------------------------------|-----|-------|-----------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5 | pF    | $V_{CC} = 5.0V$ |

| C <sub>PD</sub> | Power Dissipation Capacitance | 210 | pF    | $V_{CC} = 5.0V$ |

www.fairchildsemi.com